��(bi��o)�}: ����FPGA�Ĕ�(sh��)����ӕr��O(sh��)Ӌ�c���F(xi��n),��Դ�a,ԭ��D�cWORD��ʽՓ�� [��ӡ���]

����: wangdaling �r�g: 2018-4-2 14:03

��(bi��o)�}: ����FPGA�Ĕ�(sh��)����ӕr��O(sh��)Ӌ�c���F(xi��n),��Դ�a,ԭ��D�cWORD��ʽՓ��

�@������Altera��˾�¼���ܛ��Quartus IIӲ���_�l(f��)��팍�F(xi��n)�������ͨ�^Verilog HDLӲ���������Z�Խ�ģ���Ӵη�ģ�K�O(sh��)Ӌһ�����Еr��������犲����O(sh��)������r���[�������ModelSim�Ϸ���yԇ������������Cyclone IV E��FPGA���ƽ�_�ό��H�yԇ��C��

���Ʈ��I(y��)Փ�ģ��O(sh��)Ӌ��

�}Ŀ�� ����FPGA��24С�r��(sh��)��犵��O(sh��)Ӌ

������

���I(y��)��

�W(xu��)Ժ��

�W(xu��)̖��

��(d��o)��:

�Q��

����FPGA��24С�r��(sh��)����O(sh��)Ӌ

��ժҪ����B����verilogHDLӲ�������Z�ԽY(ji��)��FPGA��Field Programmable Gate Array�����������M(j��n)�Д�(sh��)��犵��O(sh��)Ӌ������ͨ�^��(sh��)�a�܄ӑB(t��i)�����@ʾӋ�r�Y(ji��)���������IJ��÷Ӵη�ģ�K�ķ�����������verilog�Z���M(j��n)���O(sh��)Ӌ����Quartus II 11.0�_�l(f��)ƽ�_������O(sh��)Ӌ�������g��������_���䣬��ModelSim�Ϸ�����C���������FPGAӲ�����M(j��n)�Мyԇ�����ԓ�yԇ�Y(ji��)������ԓ�O(sh��)Ӌ�����Ќ����С�

���P(gu��n)�I�~��FPGA������verilog�����Quartus II 11.0��ModelSim�����(sh��)���

Design of digital clock 24 hours based on FPGA

Medical imaging college of medical engineering professional level 2012

wangling student number: 1063451392

Instructor: he ling li

��abstract��Introducing the design of digital clock combined FPGA with verilogHDL,the time of clock can be displayed with the digital driving circuit.the project adopts the methods of Hierarchical modules to design with verilogHDL.the digital clock is designed,compiled and pin assignment on Quartus II 11.0 ,is simulated on ModelSim and is tested in the experiment box. The simulation waves and test results indicate that the project is feasible.

��key words�� FPGA; verilog; Quartus II 11.0; ModelSim; digital clock

Ŀ�

����FPGA��24С�r��(sh��)����O(sh��)Ӌ

����

1.ܛ���cverilogHDL��B

1.1ܛ������

1.2�Z�Խ�B

2.��(sh��)��犵��O(sh��)Ӌ������ԭ��

2.1�O(sh��)Ӌ����

2.2�O(sh��)Ӌԭ��

2.2.1��(sh��)��犽M�ɿ�D

2.2.2��(sh��)��犌ӴνY(ji��)��(g��u)�D

3.����ģ�K�O(sh��)Ӌ

3.1플�ģ�K

3.2��ģ�K

4.���_����

5.�·�yԇ

6.ע�����

7.�ĵ��c�w��

�������īI(xi��n)��

���x

���

���� �S���F(xi��n)����Ӽ��g(sh��)�İl(f��)չ����(sh��)����ӕr��ڼ�ͥ���܇վ���t(y��)Ժ������k���ȸ������������V���đ�(y��ng)���������ɞ��˂�����ı���Ʒ�������������a(ch��n)��ˇ�ϵ��M(j��n)������ˬF(xi��n)���ɾ����T��У�FPGA���ijɱ���ʹ��ɞ�Ŀǰ�O(sh��)Ӌ��(sh��)���·�����x����֮һ[1]��������ӕr犵ľ����h(yu��n)�h(yu��n)������ʽ犱���������犱��Ĉ�r�ܹ��ܵĻ��A(ch��)�ϲ���l(f��)չ�����T���ԄӶ��r���b����������r�V��������[��O(sh��)����������������N�����t(y��)���O(sh��)��Ķ��r�����������܃x��������C(j��)���ˣ������@Щ�����ڔ�(sh��)��犱��Ļ��A(ch��)�ό��F(xi��n)�����������·���O(sh��)Ӌ�ṩһ�����b����[1]���������ˌ����Δ�(sh��)��犵��о��ИO������x�������

1.ܛ���cverilogHDL��B1.1ܛ������ Altera® Quartus® II�O(sh��)Ӌܛ�����m�φ�оƬ�ɾ���ϵ�y(t��ng)��SOPC������ȫ����O(sh��)Ӌ�h(hu��n)��[2]�������������Ŀ��verilog HDL�ļ��O(sh��)Ӌ֮�������������ʹ�� Quartus II ܛ���е� Settings ��Ԓ������Assignment Editor �� Floorplan Editor ָ����ʼ�O(sh��)Ӌ�s���l�����������������_����������������x헺͕r��s���l��[2]�������Quartus II߀�ṩCompiler Settings ��?q��)���Assignments �ˆΣ��f(xi��)���Ñ�ָ����ʼ�O(sh��)Ӌ�ļs���l���������

ModelSim���湤����Model��˾�_�l(f��)��������֧��Verilog�������VHDL�Լ������Ļ�Ϸ��棬�����Ԍ���������ֲ���(zh��)��������ʹ�O(sh��)Ӌ��ֱ�ӿ���������һ����Ҫ��(zh��)�е��Z�䣬�����ڳ����(zh��)�е��κβ��E�κΕr�̶����Բ鿴����׃���Į�(d��ng)ǰֵ������������Dataflow�����^��ijһ��Ԫ��ģ�K��ݔ��ݔ���B�m(x��)׃����������Quartus �Ԏ��ķ��湦��(qi��ng)��Ķ�������֧��Testbench����Ŀǰ�I(y��)����ͨ�õķ�����֮һ[2]������

1.2�Z�Խ�B Verilog�Z����ʽ���Σ��cC�Z���������������������������T���_�P(gu��n)�·���������VHDL��(qi��ng)�Ķ�[3]������Ȃ��y(t��ng)�·ԭ��Dݔ�뷨�����verilogHDL�O(sh��)Ӌ���ڶ������o�茣�T���O(sh��)Ӌ�����ɺ��p�ɵČ���ɵ��O(sh��)Ӌ��ֲ����ͬ�S�ҵIJ�ͬоƬ��ȥ[3]����������ڲ�ͬҎ(gu��)ģ��(y��ng)�Õr���^����������{(di��o)���������verilog HDL����̖λ��(sh��)�Ǻ�����׃����������ʿɌ����M(j��n)���ā��m��(y��ng)��ͬ��Ҏ(gu��)ģ�㑪(y��ng)��[4]���������ڷ�����C�r������yԇ�ļ��ɲ���ͬһ�N�����Z�ԁ팦�O(sh��)Ӌ�·�M(j��n)�Мyԇ���Verilog HDL ��������ģ�K��(g��u)�ɵģ�ÿ��ģ�K�ă�(n��i)�ݶ���Ƕ��module��endmodule�ɂ��Z��֮�g������ÿ��verilog��������Ă���Ҫ���֣��˿ڶ��x��I/O�f�������(n��i)����̖������������ܶ��x�����ÿ��ģ�K���F(xi��n)�ض��Ĺ��ܣ�ģ�K�ǿ����M(j��n)�ЌӴ�Ƕ��������������������ſ��Ԍ����͵Ĕ�(sh��)���·�O(sh��)Ӌ�ָ�ɲ�ͬ��Сģ�K�팍�F(xi��n)�ض��Ĺ�����������ͨ�^플�ģ�K�{(di��o)����ģ�K�팍�F(xi��n)���w����[4]��

2.��(sh��)��犵��O(sh��)Ӌ������ԭ��2.1�O(sh��)Ӌ���� ������FPGA�錍�ƽ�_���������VerilogHDL�Z����Quartus II 11.0�_�l(f��)�h(hu��n)�����O(sh��)Ӌ��(sh��)�֕r�[5-6]����������Ӌ�r���У�r�����c��r�Ĺ����������w���ܞ飺1���܉�?q��)�С�r��������犡�����M(j��n)������Ӌ�r����ÿ�հ�24С�rӋ�r�����������Ă��߶�ʽ��(sh��)�a�������@ʾ�r�ͷ�������˂�LED���ö��M(j��n)����ʽ���@ʾ�������2�����Џ�(f��)λ�������������reset�I���Ԍ���(d��ng)ǰ�r�g���㡣3��У����������܉�?q��)��?sh��)����M(j��n)�з֕r�O(sh��)����������ڕr����e�r�M(j��n)��У����4�����c��r����������(d��ng)��12��00�r��00:00�r���������Q����1Hz���l�����12�����������c���܌��F(xi��n)���

��(sh��)��犵�Ӳ����D��D1��ʾ�����

0.png (7.76 KB, ���d��(sh��): 86)

���d����

2018-4-2 16:04 �ς�

�D1 ��(sh��)��犵�Ӳ����D

2.2�O(sh��)Ӌԭ��2.2.1��(sh��)��犽M�ɿ�D ��(sh��)�֕r犽M�ɿ�D��D2��ʾ����������Ҋ��������2��60�M(j��n)��Ӌ��(sh��)���������1��24�M(j��n)��Ӌ��(sh��)����2��2�x1��(sh��)��(j��)�x������5��ģ�K�M�������3��Ӌ��(sh��)������һ���r���̖CP���CP��50Mϵ�y(t��ng)�r犷��l���1Hz��̖�������ڕr�ͷֵ�ݔ���˽����g�a�·�����Ă���ꖘO���߶Δ�(sh��)�a���@ʾ���r�g[7] �����ݔ����8��LED�Ķ��M(j��n)����ʽ����ʾ�����ɂ��x�����քe�x��rӋ��(sh��)���ͷ�Ӌ��(sh��)����ʹ�ܿ�����̖��������r�g�M(j��n)��У���r�������ڿ��ƶ�(Adj_hour��Adj_min�������������ʹ����̖�Ӹ��ƽ�������˕rÿ��һ���r���̖��Ӌ��(sh��)����1Ӌ��(sh��)�������Ķ����F(xi��n)��С�r�ͷ�犵�У��[8]������Ӌ�r�r����ʹ����̖�����ڵ�λӋ��(sh��)�����M(j��n)λݔ���������Ӌ��(sh��)�_(d��)��59s�r���a(ch��n)��ݔ����̖(Sco=1)ʹ��Ӌ��(sh��)����1�������������Ӌ��(sh��)��ͬ�rӋ�r�����ֵ��59s 59min)�r �����a(ch��n)��ݔ����̖(Mco=1)ʹС�rӋ��(sh��)����1���

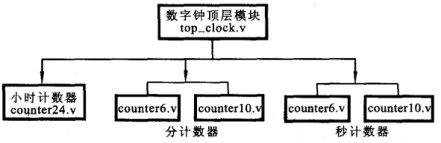

�D2 ��(sh��)��犽M�ɿ�D��Ҋ51hei������

2.2.2��(sh��)��犌ӴνY(ji��)��(g��u)�D ��(sh��)�֕r犵ČӴνY(ji��)��(g��u)�D��D3��ʾ�������Կ���������������֞�ɂ��Ӵ�4��ģ�K���������Y(ji��)��(g��u)�Ӵ���D2��ʾ����������3��ģ�K�M�ɣ�6�M(j��n)��Ӌ��(sh��)��ģ�K��counter6.v)����10�M(j��n)��Ӌ��(sh��)ģ��counter10.v)��24�M(j��n)��Ӌ��(sh��)ģ�K��counter24.v)�������플���һ��ģ�K(top_clock.v)�������{(di��o)�õӵ�3��ģ�K��ɔ�(sh��)��犵�Ӌ�r���������

�D3��(sh��)��犳���ČӴνY(ji��)��(g��u)�D

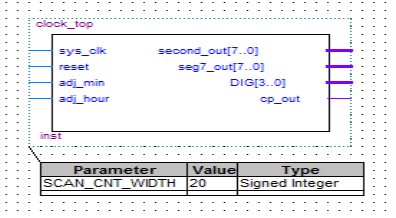

3.����ģ�K�O(sh��)Ӌ3.1플�ģ�K ������(sh��)�֕r犹���new project clock����O(sh��)Ӌ플�ģ�Ktop_clock.v��플�ģ�K����1Hz���l�·���������c��r�·����(sh��)�a�܄ӑB(t��i)����(��λ�������x��)���g�a�������@ʾ�·������플ӿ�D��D4��ʾ����

�D4 ��(sh��)���플ӿ�D

��1������1Hz�r���̖ģ�K

�r����Ӌ��(sh��)����Ӌ�r�r�cp��1Hz����̖���������ϵ�y(t��ng)�r���̖��sys_clk����50MHz���������Ҫ��50MHz��̖�M(j��n)�з��l�õ�1Hz���������w���l�Ĵ��a�飺

always@(posedge sys_clk or negedge reset) begin

if(~reset)begin

cnt<=0;cp<=0;

end else begin

if(cnt=25��d24999999)begin

cp<=~cp;cnt<=0;

end else begin

cnt<=cnt+1;

end

end

end

��2�����c��rģ�K

����Ӌ��(sh��)�r���������(d��ng)����Ӌ��(sh��)�_(d��)��59��59����������һ���r���̖cp�������ص���r���Q����1Hz���l�ʰl(f��)�����Q���F(xi��n)���c��r�������N���c�r����������Q���Ͱl(f��)��N���֡�������13�r��13�r�Ժ��ÿ�����c�����Q���l(f��)����N-12�����֡������������w���c��r���a�飺

assign hour_num=hour[7:4]*10+hour[3:0]+1;

always@(posedge cp or negedge reset)begin

if(~reset) bp_cnt_end<={5{1'b1}};

else if��hour_en��

bp_cnt_end<=((hour_num==24)?12:(hour_num>=13)?(hour_num-12):hour_num)-1;

end

always@(posedge cp or negedge reset)begin

if(~reset) bp_cnt<={5{1'b1}};

else if(hour_en) bp_cnt<=5'b0;

else if(bp_cnt<bp_cnt_end) bp_cnt<=bp_cnt+1'b1;

end

always@(posedge cp or negedge reset)begin

if(~reset) bp_enable<=1'b0;

else if(hour_en) bp_enable<=1'b1;

else bp_enable<=(bp_cnt<bp_cnt_end);

end

assign cp_out=scan_cnt[19] & bp_enable&cp;

��3��������̖ģ�K

��(sh��)��犹����������r���ÿ��һ���r���̖sys_clk��reg [SCAN_CNT_WIDTH-1:0]scan_cnt�M(j��n)�ЄӑB(t��i)������λ��B(t��i)��00�����01����10������11�����x��һ����(sh��)�a�ܣ�ֻҪ�����ٶ�����������ðl(f��)����O�ܵ�����������ҕ�X�ĕ������ã�ʹ�˸��Xÿ����(sh��)�a�ܶ����@ʾ��������w������a�飺

always@(posedge sys_clk or negedge reset)

begin

if(~reset)

scan_cnt<=0;

else begin

scan_cnt<=scan_cnt+1;

end

end

always@(*)

begin

case(scan_cnt[SCAN_CNT_WIDTH-1:SCAN_CNT_WIDTH-2])

2'b00:begin DIG_r<=4'b0001; scan_out<=minute[3:0];end

2'b01:begin DIG_r<=4'b0010; scan_out<=minute[7:4];end

2'b10:begin DIG_r<=4'b0100; scan_out<=hour[3:0];end

2'b11:begin DIG_r<=4'b1000; scan_out<=hour[7:4];end

default:begin DIG_r<=4'b0000;scan_out<=4'b0;end

endcase

end

��4���x���@ʾ��(sh��)��(j��)���g�aģ�K

������̖�Q��ijһ�r����һ����(sh��)�a�ܱ��c���������������̖Ҳ���@ʾ�r�g��(sh��)��(j��)���x����̖������ڕr�g��(sh��)��(j��)��BCD�a��ʽ����������g���߶��@ʾ�a�������w���a�飺

always@(*)

begin

case (scan_out)

0: seg7_out_r = 7'b0111111; // 0

1: seg7_out_r = 7'b0000110; // 1

2: seg7_out_r = 7'b1011011; // 2

3: seg7_out_r = 7'b1001111; // 3

4: seg7_out_r = 7'b1100110; // 4

5: seg7_out_r = 7'b1101101; // 5

6: seg7_out_r = 7'b1111101; // 6

7: seg7_out_r = 7'b0100111; // 7

8: seg7_out_r = 7'b1111111; // 8

9: seg7_out_r = 7'b1100111; // 9

10: seg7_out_r = 7'b1110111; // A

11: seg7_out_r = 7'b1111100; // b

12: seg7_out_r = 7'b0111001; // c

13: seg7_out_r = 7'b1011110; // d

14: seg7_out_r = 7'b1111001; // E

15: seg7_out_r = 7'b1110001; // F

default: seg7_out_r = 7'b0000000;

endcase

end

��4���Y(ji��)���@ʾģ�K

assign seg7_out={1'b0,(~seg7_out_r[6:0])};

assign DIG=~DIG_r[3:0];

assign second_out=second[3:0]+second[7:4]*10;

��5���֕rУ�?z��i)��K

ʹ�ܶˣ�en����������(f��)λ��reset������ƽ�r��Ч��Ӌ��(sh��)������Ӌ�r���֕rУ�adj_min,adj_hour ����ƽ�r(������_�l(f��)�匢�ܴa�_�P(gu��n)�ܵ�off��B(t��i))ֹͣӋ�r�˕r��(sh��)�a��̎���{(di��o)����B(t��i)��ÿ��һ�딵(sh��)�a�ֺܷ͕r�Ĕ�(sh��)���@ʾ����1�һ���Ӱ푣������֕rУ����ƽ�rӋ��(sh��)������Ӌ�r������w�֕rУ���a�飺

assign minL_en=adj_min?vdd:(second==8'h59);

assign minH_en=(adj_min&&(minute[3:0]==4'h9))||(minute[3:0]==4'h9)&&(second==8'h59);

assign hour_en=adj_hour?vdd:((minute==8'h59)&&(second==8'h59));

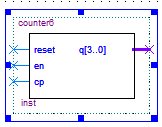

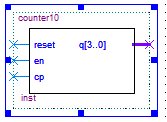

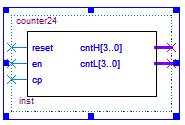

3.2��ģ�K �O(sh��)Ӌ6�M(j��n)��Ӌ��(sh��)��ģ�K��counter6.v����10�M(j��n)��Ӌ��(sh��)��ģ�K��counter10.v����24�M(j��n)��Ӌ��(sh��)��ģ�K��counter24.v�����Ӌ��(sh��)�Y(ji��)����BCD�a��ʽ��ͨ�^�{(di��o)���@����Ԫ�����Ԍ��F(xi��n)Ӌ�r����(d��ng)ʹ�ܶ�en��ncr����ƽ�r�����ÿ��һ���}�_�����Ӌ��(sh��)��q��1ֱ��Ӌ�M���㣩�����ģ�K��D��D5���£�

�D5 6�����10���24�M(j��n)��ģ�K��D

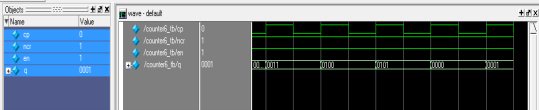

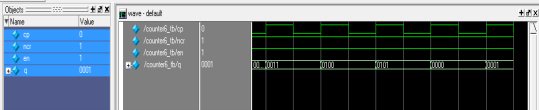

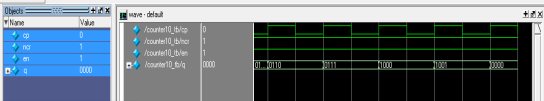

��1��6�M(j��n)��Ӌ��(sh��)��ģ�K���沨�μ����a���F(xi��n)

�D6 6�M(j��n)��Ӌ��(sh��)����

�D6 6�M(j��n)��Ӌ��(sh��)����

module counter6 (q,reset,en,cp);

input cp,reset,en;

output[3:0]q;

reg[3:0]q;

always@(posedge cp or negedge reset)

begin

if(~reset)q<=4'b0000;

else if (~en)q<=q;

else if(q==4'b0101)q<=4'b0000;

else q<=q+1'b1;

end

endmodule

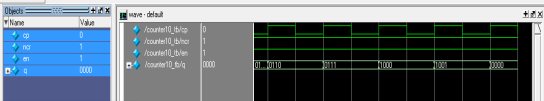

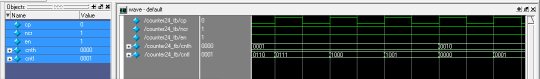

��2��10�M(j��n)��Ӌ��(sh��)��ģ�K���沨�μ����a���F(xi��n)

�D7 10�M(j��n)��Ӌ��(sh��)����

�D7 10�M(j��n)��Ӌ��(sh��)����module counter10 (q,reset,en,cp);

input cp,reset,en;

output[3:0]q;

reg[3:0]q;

always@(posedge cp or negedge reset)

begin

if(~reset)q<=4'b0000;

else if(~en)q<=q;

else if(q==4'b1001)q<=4'b0000;

else q<=q+1'b1;

end

endmodule

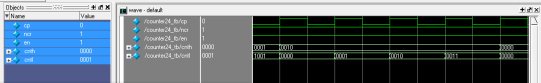

��3��24�M(j��n)��Ӌ��(sh��)��ģ�K���沨�μ����a���F(xi��n)

�D8 24�M(j��n)��Ӌ��(sh��)����

module counter24(cntH,cntL,reset,en,cp);

input cp,reset,en;

output [3:0] cntH,cntL;

reg[3:0]cntH,cntL;

always@(posedge cp or negedge reset)

begin

if(~reset){cntH,cntL}<=8'h00;

else if(~en)

{cntH,cntL}<={cntH,cntL};

else if ((cntH>2)||(cntL>9)||((cntH==2)&&(cntL>=3)))

{cntH,cntL}<=8'h00;

else if ((cntH==2)&&(cntL<3))

begin

cntH<=cntH;

cntL<=cntL+1'b1;

end

else if(cntL==9)

begin

cntH<=cntH+1'b1;

cntL<=4'b0000;

end

else

begin

cntH<=cntH;

cntL<=cntL+1'b1;

end

end

endmodule

4.���_���� �x��Ŀ��(bi��o)������������(y��ng)�����_�M(j��n)���i���������@�����x���������Altera��˾Cyclone Eϵ�е�EP4C6E22C8оƬ���������_���䷽�����1��

ע���ڹ��_����r���F(xi��n)PGA��101���_�����F(xi��n)���F(xi��n)Error: Can't place multiple pins assigned to pin location Pin_XX (IOC_X28_Y2_N0)

��Q������

Assignments->Device->Device and pin options->(��)Dual purpose pin��nCE0�Լ�Other Active Parallel Pins(������(f��)�õĹ��_)ȫ���O(sh��)�øĞ飺 ��use as regular IO��Ĭ�J(r��n)ֻ�oFPGA���dʹ���x���(f��)���˾������d��߀���Խo��ͨIOʹ�á�

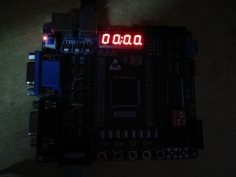

��1 ���_���䷽��

5.�·�yԇ ����C�O(sh��)Ӌ�·�����������d��FPGA�_�l(f��)�����M(j��n)��Ӳ���yԇ������dĿ��(bi��o)�����x��Alter��˾��Cyclone IV Eϵ�е�EP4C6E22C8оƬ,��Quartus II 11.0 ܛ���M(j��n)���·�C�ϼ��������d�������������_�O(sh��)���������پ��gһ���������K���ɿ������d��Ŀ��(bi��o)�ļ�������������O(sh��)��������(y��ng)���_�͔�(sh��)�a���(q��)���·�M(j��n)���B�ӣ����Ŀ��(bi��o)�ļ����d��������(d��ng)����������t��(sh��)�a���@ʾӋ�r�Y(ji��)�����܌��F(xi��n)�֕rУ������ͨ�^�yԇӋ�r�Y(ji��)���c�֕rУ����_������

6.ע�������1������^���аl(f��)�F(xi��n)��(sh��)�a�ܲ��ֹ��ӵĕr����?x��)r����(d��o)��(sh��)�ֵ��@ʾ�������������������(sh��)�a�ܵĒ����l�ʞ�ϵ�y(t��ng)�}�_50MHz��������FPGA��(sh��)�a�ܵĒ����l�ʲ�֧��̫���l�ʻ����ǔ�(sh��)�a�ܵĹ��_��֧��̫���l�����ђ����l�ʽ������ɣ�����������������l�ʵ�λ�������������λ�����x��Խ����������l��Խ�ͣ�������Ą����£�

reg[7:0]scan_out��reg[19:0]scan_out

case(scan_cntt[7:6])��case(scan_cnt[19:18])

�@�Ӽ��ɽ�Q��(sh��)�a���@ʾ����Ć��}�������

- ���^�쌍���^���Ќ�if��cnt==24999999���ij�if(��cnt==25000000/k��-1)���Ɍ��r�g�߿�k�������^�쌍�Y(ji��)�����

7.�ĵ��c�w�� ����Փ�ďIJ���īI(xi��n)���Y(ji��)�ό��H�x�}�����ܛ�����b���Ɍ�ʩ�������O(sh��)Ӌ�������VerilogHDL�ľ���,�����ǵ�һ�������Ӳ�������O(sh��)Ӌ��

���ȣ����O(sh��)Ӌ˼·�ϴ��ڇ�(y��n)��ģ������߉��y�������������플�ģ�K���O(sh��)Ӌ�r��������ģ�K֮�g����P(gu��n)ϵ���������һЩ��������ȱ����(zh��n)�_���J(r��n)�R�������

��Σ���ܛ���İ��b�������h(hu��n)���IJ���Ϥ��(d��o)����M(j��n)�еľ������

��������һ�}���ԌW(xu��)VerilogHDL�Z�Գ�����һЩ�ͼ����Z���e�`����ʹ��һ����(bi��o)�c����ƥ�䆖�}�������(sh��)��(j��)��Ͷ��x�e�˶�����(d��o)��һ�B�����e�`����������ھ��̕rһ��Ҫ�����м�(x��)������

���ģ��ڷ��沨�ε��^���c���������@�е����I(y��)֪�R�IJ������������ڌ����l���������������g�a���@ʾ�·�@�K���ڒ����l������ӕr��λ���r�g���ȼ��\(y��n)�Еr�g�]���O(sh��)Ӌ�Ì�(d��o)�o���^�쌍����_(d��)���IJ��μ��@ʾ�Y(ji��)��������

���壺�˴�Փ���O(sh��)Ӌ�r�g�}���һ��A(ch��)����]���M(j��n)һ������(sh��)�֕r犵Ĺ��ܔU(ku��)չ��

����������Ǚz�ԭ��������Ψһ����������ֻ��ͨ�^����ćLԇ���^����������������ܵõ����_�Č��Y(ji��)��������

��˴�Փ��Ҳ�ի@�ܶ࣬�W(xu��)��(x��)�˔�(sh��)��ϵ�y(t��ng)���϶��µ��O(sh��)Ӌ����������M(j��n)һ����Ϥ�Ӵ��·���O(sh��)Ӌ����������픶��µ�����O(sh��)Ӌ������ʹ����֮�g�l�������������ֹ����_������������O(sh��)Ӌ�����ͬ�rҲ���B(y��ng)���Լ������O(sh��)Ӌ������������Ӌ��C(j��)ܛ�����̑�(y��ng)�÷�����dȤҲ����ČW(xu��)��(x��)��û��A(ch��)����

�������īI(xi��n)��[1]���A��,�u�۱�.����Ӽ��g(sh��)���A(ch��)��(sh��)�ֲ��֣�����棩��[M].����:�ߵȽ���������,2005144-146,162-163,121-133.

[2]�����.Alter FPGA ���̎����L�փ�[M].����:���A��W(xu��)������,2012.

[3]����.verilog����֪�R���£�[J].��Ӯa(ch��n)Ʒ����,2002,��20��:87-90.

[4]����.��verilog��(sh��)��ϵ�y(t��ng)�O(sh��)Ӌ�̡̳�[M].����:�������պ����W(xu��),2004���.

[5]�o(j��)��Ȼ,��һ,����Դ.����FPGA�Ķ�ܔ�(sh��)����O(sh��)Ӌ[J].

����O(sh��)Ӌ����,2012,20��16):177-179.

JI Xin-ran,DING Yi,LIANG Zhi-yuan.Design of

multifunction digital clock based on FPGA [J].Electronic

Design Engineering,2012,20��16��:177-179.

[6]����t.����FPGA���F(xi��n)�Ĕ�(sh��)����O(sh��)Ӌ[J].��Ϣ���g(sh��).

[7]��܊.����FPGA��SOPC���`�̳�[M].����:�ƌW(xu��)������,2010.

[8]����,�ξ�.����FPGA�Ĕ�(sh��)�������O(sh��)Ӌ[J].����O(sh��)Ӌ����,2014,22(4):127-129

���x ����Փ�ĵ����������Ҫ���x�ҵ�ָ��(d��o)�ώ�--�������ώ�����������x�}�����������c˼·�ٵ�����Փ�ĵ�����������ڴ����g���ܴ��СС�Ć��}���ֻҪ�҆��������ώ�������һ�r�g�����䟩�Ğ��ҽ���������ώ��J(r��n)��ؓ(f��)؟(z��)�Ľ̌W(xu��)�����c�㌍��Ʒ�|(zh��)�����Ӱ������������]�ҿ��Ё����ð��c̓�٣�һ��Ҫ�_̤������ʲô����ʲô�����Σ����x�����īI(xi��n)�������ᵽ�ķ����c�^�c������������x�����ߵ����P(gu��n)�����Ҍ��Ӵ��·���O(sh��)Ӌ�����M(j��n)һ�����J(r��n)�R����u��Ϥ��verilog�Z�Եľ����L(f��ng)���������Ȼ����Ҫ���x�H�۵�ͬ�W(xu��)�������������ゃ������c�Ą�ʹ��׃�Èԏ�(qi��ng)�c���㣬����Ҳ�dz����x�W(w��ng)�ϟ���Փ�������ṩ�Ď����ͽ���������������ڌ��I(y��)֪�R���������Փ����߀���ںܶ�覴ú���Ҫ�о����M(j��n)�ĵط����������ώ���ͬ�W(xu��)����ָ������ٴθ��x������ώ���ՁՁ�̌�(d��o)�����xͬ�W(xu��)�Ď����c�P(gu��n)�����ף���ҵ��ώ������䐂���H���Ҹ���������ҵ�ͬ�W(xu��)������������ʸ߷����

������DƬ��

�����a��

0.jpg (23.66 KB, ���d��(sh��): 117)

���d����

2018-4-2 16:07 �ς�

��������

��������

������Word��ʽ�ęn51�����d��ַ����(n��i)�������DƬ�cԴ���a����

����FPGA�Ĕ�(sh��)����ӕr��O(sh��)Ӌ�c���F(xi��n).doc

(6.21 MB, ���d��(sh��): 211)

����FPGA�Ĕ�(sh��)����ӕr��O(sh��)Ӌ�c���F(xi��n).doc

(6.21 MB, ���d��(sh��): 211)

2018-4-2 13:53 �ς�

�c���ļ������d����

���d�e��: �ڎ� -5

����: chenjunwycj �r�g: 2020-6-17 17:29

���e��ֵ�����d�W(xu��)��(x��)�������

| �gӭ���R (http://www.torrancerestoration.com/bbs/) |

Powered by Discuz! X3.1 |

�D6 6�M(j��n)��Ӌ��(sh��)����

�D6 6�M(j��n)��Ӌ��(sh��)���� �D7 10�M(j��n)��Ӌ��(sh��)����

�D7 10�M(j��n)��Ӌ��(sh��)����

����FPGA�Ĕ�(sh��)����ӕr��O(sh��)Ӌ�c���F(xi��n).doc

(6.21 MB, ���d��(sh��): 211)

����FPGA�Ĕ�(sh��)����ӕr��O(sh��)Ӌ�c���F(xi��n).doc

(6.21 MB, ���d��(sh��): 211)