標題: Cortex-M0處理器兼容 功能 指令集映射詳解 [打印本頁]

作者: heila 時間: 2015-12-9 02:36

標題: Cortex-M0處理器兼容 功能 指令集映射詳解

本帖最后由 heila 于 2015-12-9 02:37 編輯

來自于ARM上的消息:

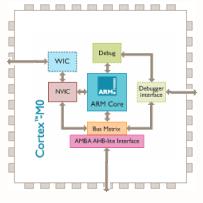

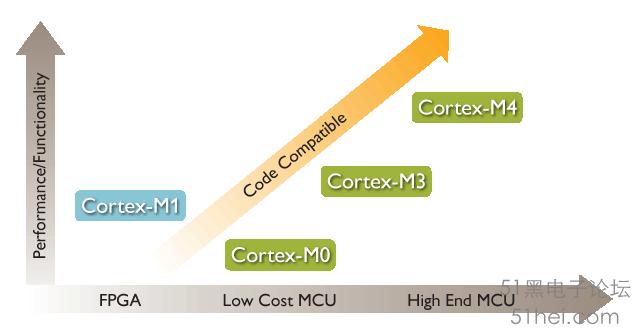

ARM Cortex?6?4-M0 處理器是現(xiàn)有的最小����、能耗最低和能效最高的 ARM 處理器。該處理器硅面積極小�����、能耗極低并且所需的代碼量極少���,這使得開發(fā)人員能夠以 8 位的設(shè)備實現(xiàn) 32 位設(shè)備的性能,從而省略 16 位設(shè)備的研發(fā)步驟�����。Cortex-M0 處理器超低的門數(shù)也使得它可以部署在模擬和混合信號設(shè)備中��。

ARM Cortex-Mx兼容

ARM Cortex-M0 功能| Cortex-M0 |

| 體系結(jié)構(gòu) | ARMv6-M(馮諾依曼) |

| ISA 支持 | Thumb?0?3/ Thumb-2 技術(shù)* |

| 管道 | 3 階段 |

| Dhrystone | 0.9 DMIPS/MHz |

| 中斷 | NMI + 1 到 32 個物理中斷 |

| 中斷延遲 | 16 個周期 |

| 睡眠模式 | 集成的 WFI 和 WFE 指令

睡眠和深度睡眠信號

隨電源管理工具包提供的可選保留模式 |

| 增強的指令 | 單周期 (32x32) 乘法 |

| 調(diào)試 | JTAG 或串行線調(diào)試端口 |

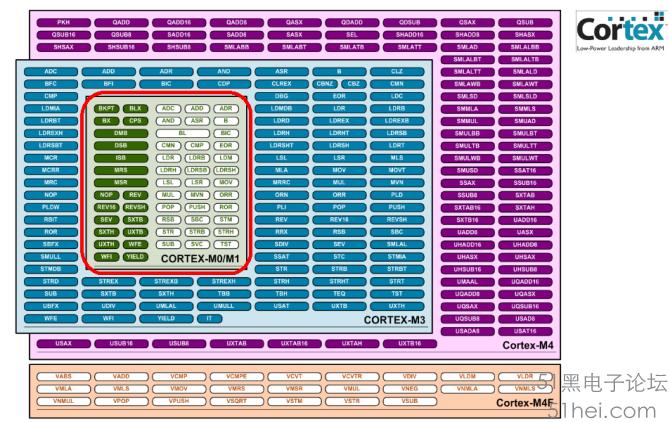

* ARM Cortex-M0 處理器執(zhí)行 Thumb 指令集���,包括少量使用 Thumb-2 技術(shù)的 32 位指令���。這是 ARM Cortex-M3 和 ARM Cortex-M4 支持的指令集的二進制向上可兼容子集。

ARM Cortex-Mx指令集映射

| 歡迎光臨 (http://www.torrancerestoration.com/bbs/) |

Powered by Discuz! X3.1 |