��(bi��o)�}: FPGA Verilog�Z(y��)���������xֵ�c�������xֵ��(g��)�˿��� [��ӡ���(y��)]

����: ��Ӻ� �r(sh��)�g: 2016-6-27 01:10

��(bi��o)�}: FPGA Verilog�Z(y��)���������xֵ�c�������xֵ��(g��)�˿���

��������������������FPGA Verilog�Z(y��)���������xֵ�c�������xֵ�^(q��)�e�Ă�(g��)�˿���

����������������������������������������������-------�������c���˲���ͬ����

��(du��)��Verilog ���W(xu��)�߁�(l��i)�f(shu��)�����������xֵ�c�������xֵ��(y��ng)ԓҪ�^(q��)�eһ��������ҹ�Ӌ(j��)��(du��)���@�ɷN�xֵ��ʽ�đ�(y��ng)�ý��f(shu��)������ʲô�r(sh��)��ԓ�������xֵ��ʲô�r(sh��)��ԓ�÷������xֵ��ͨ��Ҋ����һ��Ԓ�������r(sh��)��߉����ͨ���÷������xֵ������M��߉����ͨ��ʹ�������xֵ������������@��Ȼ�Ǻ�������������Ҳ������ζ���r(sh��)��߉����Ͳ����������xֵ�ˣ��M��߉����Ͳ������÷������xֵ�������������X(ju��)���б�ҪŪ���һ�������xֵ�ͷ������xֵ�ļ�(x��)�^(q��)�e���

����߀�ǻؚw�¶��x�����^�����xֵ����������� a=b; ��(d��ng)�@��(g��)�xֵ�Z(y��)���(zh��)�еĕr(sh��)���Dz����S�������Z(y��)���(zh��)�е��������@����������ԭ���������xֵ�����������a<=b;��(d��ng)�@��(g��)�xֵ�Z(y��)���(zh��)�еĕr(sh��)���Dz���K�����Z(y��)���(zh��)�еġ���(du��)��FPGA��(l��i)�v��������Ƭ�C(j��)��ȣ���ʹ�Ǹ��ن�Ƭ�C(j��)���������������ă�(y��u)�c(di��n)���Z(y��)���(zh��)�еIJ����ԣ�����Ƭ�C(j��)�Z(y��)���(zh��)��������(zh��)�е������������f(shu��)�҂�Ҫ������ú�FPGA�@��(g��)��(y��u)�c(di��n)����ô�҂���(y��ng)ԓ�M��ʹ�÷������xֵ�����

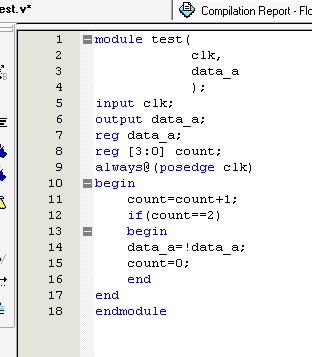

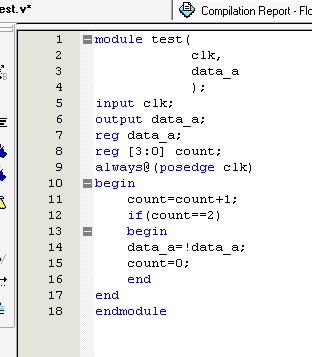

���������һ��(g��)��(ji��n)�ε����Ӂ�(l��i)�\��һ���ߵą^(q��)�e������

�@��һ��(g��)��(ji��n)�εķ��l���������Ŀ���nj�clk�r(sh��)��ķ��l������Count��ʼֵ��0,����(g��)�˽�(j��ng)�(y��n)�J(r��n)���������?y��n)?font face="Times New Roman">verilog�����ƺ��](m��i)����(du��)׃���M(j��n)�г�ʼ���������Ȼ���һ��(g��)�r(sh��)犵������ص���(l��i)�r(sh��)�������count�Լ�1��׃����1�����if�Z(y��)���(zh��)�О�٣�Ȼ��ڶ���(g��)�r(sh��)������ص���(l��i)�r(sh��)������count���Լ�1׃����2��if�Z(y��)���(zh��)�Зl��������������t��(zh��)��if�Z(y��)���(n��i)�ă�(n��i)�����������data_a��(sh��)��(j��)���D(zhu��n)�������count�����xֵ��0���������ԓ�������ÿ?j��)ɂ�(g��)�r(sh��)犵��������������data_a��(sh��)��(j��)���D(zhu��n)һ�������õ��ķ��l��Ч���������

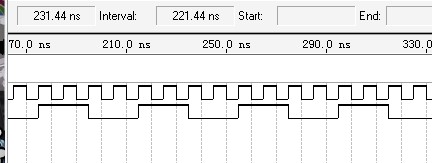

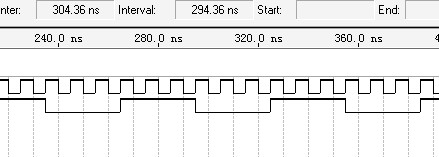

�D����沨�����������ȫ��(du��)��ס���������

����ij����õ��������xֵ�����Ҳ���� count��(zh��)���Լ�1�ĕr(sh��)�����������κ��Z(y��)�䶼�Dz��܈�(zh��)�е��������@������c(di��n)���Ƭ�C(j��)�����C�Z(y��)��������һ��(g��)����(zh��)�е�always�K������

���������ij����xֵȫ�ijɷ������xֵ����Ч����(hu��)�����أ�

�����҂��Ȳ���������������Ȍ�(du��)��һ�·��沨���������

�ķ��沨��(l��i)���������@��(g��)����_׃���ˌ�(du��)clk�r(sh��)犵������l���@Ȼ�����҂�֮ǰ��˼·�����Y(ji��)��������(sh��)�H�������@���ӈ�(zh��)�е������

���ȿ����@�����������1���������xֵ��always�K�Y(ji��)�����xֵ�����������(g��)�������dz���Ҋ��always�K�ĽY(ji��)����(bi��o)ӛend����xֵ�����Dz���������(d��ng)�������_ʼ����ԓ�Z(y��)��r(sh��)�](m��i)���κ΄�(d��ng)�����������ȰѺ����ֵ�oӋ(j��)�����(l��i)����һ��(g��)�Ĵ����Е���������ˉK�Y(ji��)�����xֵ�����������е��Ȱ�count+1Ӌ(j��)�����(l��i)������������ˉK�Y(ji��)���Ű��ǂ�(g��)�Y(ji��)���xֵ�ocount�����2��������������xֵ�Dz��Ј�(zh��)�е���������˲����ж��ق�(g��)always�K���������ÿ��(g��)always�K�����ж��ٗl�������xֵ������������˲�gһ�K���Ј�(zh��)�е���������ɔ_�������

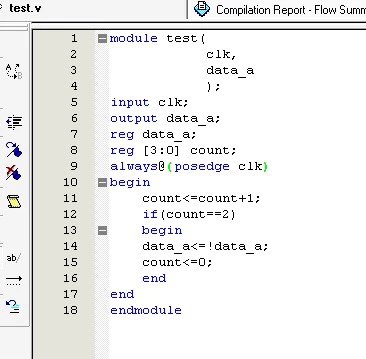

��������ij���ͺ÷�����

Count��ʼֵ��0�����һ��(g��)�r(sh��)犵������ص���(l��i)�r(sh��)�����count<=count+1 �@�l�Z(y��)���Ȳ��xֵ��ǰ���f(shu��)�ˉK�Y(ji��)�����xֵ��������count+1�ѽ�(j��ng)Ӌ(j��)�����(l��i)���ڼĴ����д惦(ch��)����������Ȉ�(zh��)�е���if�Z(y��)��������if�Z(y��)��˕r(sh��)�l����Ȼ�ǣ�count=0�����l���������������(zh��)��if��(n��i)���Z(y��)�䣬��������always�K�Y(ji��)����(bi��o)ӛend��������@�ň�(zh��)��count<=���xֵ�����count�˕r(sh��)��1�����Ȼ��ڶ���(g��)�r(sh��)������ص���(l��i)�����ͬ���Ȉ�(zh��)��if�Z(y��)�䣬�l����Ȼ����������Ȼ���و�(zh��)��count�Լ�1������count׃?y��u)?font face="Times New Roman">2��������(g��)�r(sh��)������ص���(l��i)�������Ȉ�(zh��)��if�Z(y��)�䣬�l���M�����������ڴ˕r(sh��) ������(g��)�������xֵ���Z(y��)����F(xi��n)

count<=count+1;

data_a<=!data_a;

count<=0;

�@����(g��)�Z(y��)�䰴�����vҲ�Dz��Ј�(zh��)�еģ�������������Ѓɂ�(g��)�Z(y��)��ͬ�r(sh��)��(du��)count�M(j��n)�����xֵ����������ôզ���أ��@�c(di��n)�P����δ����������Ո(q��ng)�_(d��)�˽�����������ߴ��պ�P��Ū����ځ�(l��i)�������������������

7��25�������(j��ng)�^(gu��)�����c(di��n)�������������(w��n)�}�K������һ��(g��)�����Ľ������

����S���Y�Ͽ��Եó��ĽY(ji��)Փ�ǣ���begin �������end �з������xֵ��(sh��)�H���Dz����е�����(zh��)�С���Ԓ������������begin �����������end �Z(y��)��K�е÷������xֵ�Z(y��)���c�����K�еķ������xֵ�Z(y��)���Dz��е����������nj�(du��)�چ�(g��)begin ������end �K�е��Z(y��)��s������(zh��)�е�����������verilog�Z(y��)�����Dz����S�ڃɂ�(g��)�K�Ќ�(du��)ͬһ׃���M(j��n)���xֵ���������چ�һ�K�������������Ѓɂ�(g��)��ɂ�(g��)���ϵķ������Z(y��)�䌦(du��)ͬһ��(g��)׃���M(j��n)�����xֵ���������ôԓ׃����ֵ�����һ��(g��)�Z(y��)�����Q����

����: 32323232 �r(sh��)�g: 2016-7-3 16:38

�x�x ��� ���ý�Q��������ɻ�

| �gӭ���R (http://www.torrancerestoration.com/bbs/) |

Powered by Discuz! X3.1 |