|

xuyaqi 發(fā)表于 2020-4-17 15:37 謝謝你 |

|

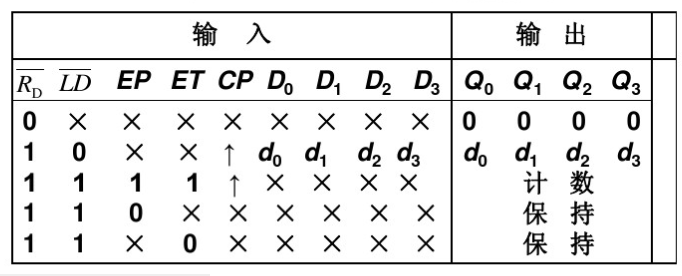

module fidv1 (rd,clk,et,load,datain,dataout,cout,ep); input rd,et,load,clk,ep; input [3:0] datain; output [3:0] dataout ; output cout; reg cout; reg [3:0] q1; wire rd; always @ (posedge clk or negedge rd) if (rd==0) begin q1<=4'd0; end//rd=0時清零 else begin if(clk==1&load==0) q1=datain; else if(clk==1&load==1) begin if(ep==1&et==1&q1<4'd10) //開始計數 begin q1=q1+1;cout=0; end else if((ep&et)==0) begin q1=q1;cout=0;end//保持不變 else if(q1==4'd10) cout=1;//進位輸出 end end assign dataout =q1; endmodule |