復(fù)位

有三種復(fù)位:系統(tǒng)復(fù)位、電源復(fù)位和后備域復(fù)位

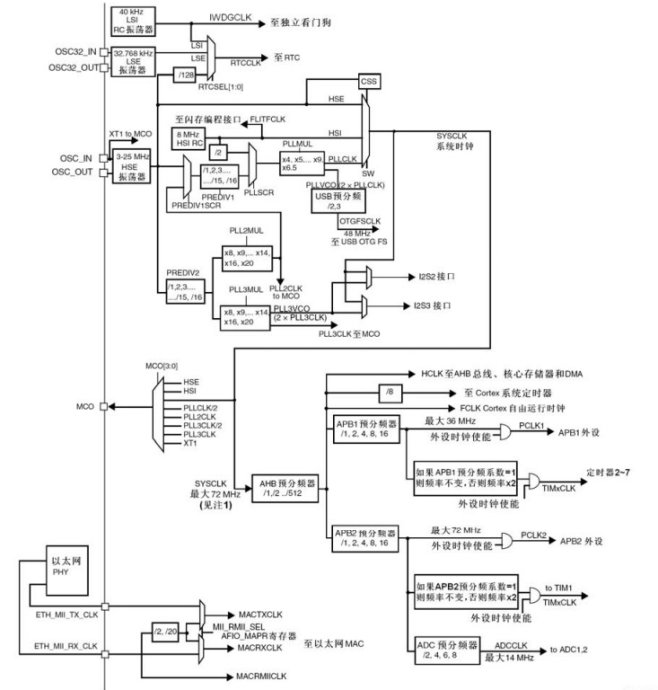

時(shí)鐘

三種不同的時(shí)鐘源可被用來(lái)驅(qū)動(dòng)系統(tǒng)時(shí)鐘(SYSCLK)

● HSI振蕩器時(shí)鐘

● HSE振蕩器時(shí)鐘

● PLL 時(shí)鐘

這些設(shè)備有以下2種二級(jí)時(shí)鐘源:

● 40kHz 低速內(nèi)部RC(LSI RC)振蕩器,可以用于驅(qū)動(dòng)獨(dú)立看門(mén)狗�����,或通過(guò)程序選擇驅(qū)動(dòng)RTC,用于從停機(jī)/ 待機(jī) 模式下自動(dòng)喚醒系統(tǒng)�。

● 也可以通過(guò)程序選擇32.768kHz 低速外部晶體(LSE晶體)用來(lái)驅(qū)動(dòng)RTC(RTCCLK)。

當(dāng)不被使用時(shí)����,任一個(gè)時(shí)鐘源都可被獨(dú)立地啟動(dòng)或關(guān)閉,由此優(yōu)化系統(tǒng)功耗���。

從下圖看出有:

LSI(40KHz的內(nèi)部低速時(shí)鐘)

LSE(32.768KHz的外部時(shí)鐘)

HSE (3-25M的外部輸入高速時(shí)鐘)

HSI (8M的內(nèi)部高速時(shí)鐘)

系統(tǒng)時(shí)鐘SYSCLK經(jīng)過(guò)AHB分頻后可以直接給AHB���、DMA等用,或者再經(jīng)過(guò)APB1或APB2的分頻再給外設(shè)使用���。

除去以下情況�,所有外設(shè)的時(shí)鐘都是從系統(tǒng)時(shí)鐘(SYSCLK) 得到:

● Flash存儲(chǔ)器編程接口時(shí)鐘始終是HSI時(shí)鐘

● 全速USB OTG的48MHz時(shí)鐘是從PCC VCO時(shí)鐘(2xPLLCLK) ����,和隨后可編程預(yù)分頻器(除3或除2) 得到,這是通 過(guò)RCC_CFGR寄存器的OTGFSPRE位控制�����。為了正常地操作USB全速OTG�����,應(yīng)該配置PLL 輸出72MHz或48MHz�����。

● 全速USB OTG的48MHz時(shí)鐘是從PCC VCO時(shí)鐘(2xPLLCLK) ��,和隨后可編程預(yù)分頻器(除3或除2) 得到��,這是通 過(guò)RCC_CFGR寄存器的OTGFSPRE位控制��。為了正常地操作USB全速OTG�����,應(yīng)該配置PLL 輸出72MHz或48MHz。

● I2S2和I2S3的時(shí)鐘還可以從PLL3 VCO 時(shí)鐘(2xPLL3CLK)得到�,這是通過(guò)RCC_CFGR2寄存器的I2SxSRC位制。 更多有關(guān)PLL3的內(nèi)容和如何配置I2S 時(shí)鐘����,以得到高質(zhì)量的音頻效果,請(qǐng)參閱第23.4.381/754 節(jié):時(shí)鐘發(fā) 生器��。

● 以太網(wǎng)MAC的時(shí)鐘(TX ����、RX和RMII)是由外部PHY提供。更多有關(guān)以太網(wǎng)配置的詳情����,請(qǐng)見(jiàn)

第27.4.4 MII/RMII的選擇 節(jié): 。

當(dāng)使用以太網(wǎng)模塊時(shí)�,AHB時(shí)鐘頻率必須至少為25MHz。

RCC通過(guò)AHB時(shí)鐘(HCLK)8 分頻后作為Cortex 系統(tǒng)定時(shí)器(SysTick)的外部時(shí)鐘��。通過(guò)對(duì)SysTick控制與狀態(tài)寄存器的設(shè)置���,可選擇上述時(shí)鐘或Cortex(HCLK)時(shí)鐘作為SysTick時(shí)鐘�。ADC時(shí)鐘由高速APB2時(shí)鐘經(jīng)2、4 ��、6或8分頻后獲得�。 定時(shí)器時(shí)鐘頻率分配由硬件按以下2種情況自動(dòng)設(shè)置:

1. 如果相應(yīng)的APB預(yù)分頻系數(shù)是1,定時(shí)器的時(shí)鐘頻率與所在A(yíng)PB 總線(xiàn)頻率一致�����。

2. 否則����,定時(shí)器的時(shí)鐘頻率被設(shè)為與其相連的APB 總線(xiàn)頻率的2倍�。

FCLK是Cortex??-M3的自由運(yùn)行時(shí)鐘。

HSE時(shí)鐘

高速外部時(shí)鐘信號(hào)(HSE) 由以下兩種時(shí)鐘源產(chǎn)生:

● HSE外部晶體/ 陶瓷諧振器

● HSE用戶(hù)外部時(shí)鐘

為了減少時(shí)鐘輸出的失真和縮短啟動(dòng)穩(wěn)定時(shí)間�����,晶體/ 陶瓷諧振器和負(fù)載電容器必須盡可能地靠近振蕩器引腳���。負(fù)載電容值必須根據(jù)所選擇的振蕩器來(lái)調(diào)整����。

HSI時(shí)鐘

HSI時(shí)鐘信號(hào)由內(nèi)部8MHz 的RC振蕩器產(chǎn)生��,可直接作為系統(tǒng)時(shí)鐘或在2分頻后作為PLL 輸入。 HSI RC振蕩器能夠在不需要任何外部器件的條件下提供系統(tǒng)時(shí)鐘��。它的啟動(dòng)時(shí)間比HSE晶體振蕩器短�����。然而�����,即使在校準(zhǔn)之后它的時(shí)鐘頻率精度仍較差�。

PLL

主PLL 以下述時(shí)鐘源之一為輸入,產(chǎn)生倍頻的輸出:

● HSI時(shí)鐘除以2

● HSE或通過(guò)一個(gè)可配置分頻器的PLL2時(shí)鐘

LSE 時(shí)鐘

LSE 晶體是一個(gè)32.768kHz 的低速外部晶體或陶瓷諧振器�。它為實(shí)時(shí)時(shí)鐘或者其他定時(shí)功能提供

一個(gè)低功耗且精確的時(shí)鐘源。

LSI時(shí)鐘

系統(tǒng)時(shí)鐘(SYSCLK) 選擇

/////////////////////////////////////

寄存器介紹 0x4002 1000 - 0x4002 13FF 復(fù)位和時(shí)鐘控制(RCC)

時(shí)鐘控制寄存器(RCC_CR) -->內(nèi)外部各種時(shí)鐘的使能��,各個(gè)PLL的使能等

時(shí)鐘配置寄存器(RCC_CFGR)-->配置各個(gè)時(shí)鐘的分頻系數(shù)以及PLL的分配系數(shù)以及時(shí)鐘源的選擇等

時(shí)鐘配置寄存器(RCC_CFGR2)-->配置各個(gè)時(shí)鐘的分頻系數(shù)以及PLL的分配系數(shù)以及時(shí)鐘源的選擇等