STM32F103系列增強(qiáng)型微控制器

——時鐘控制(RCC)

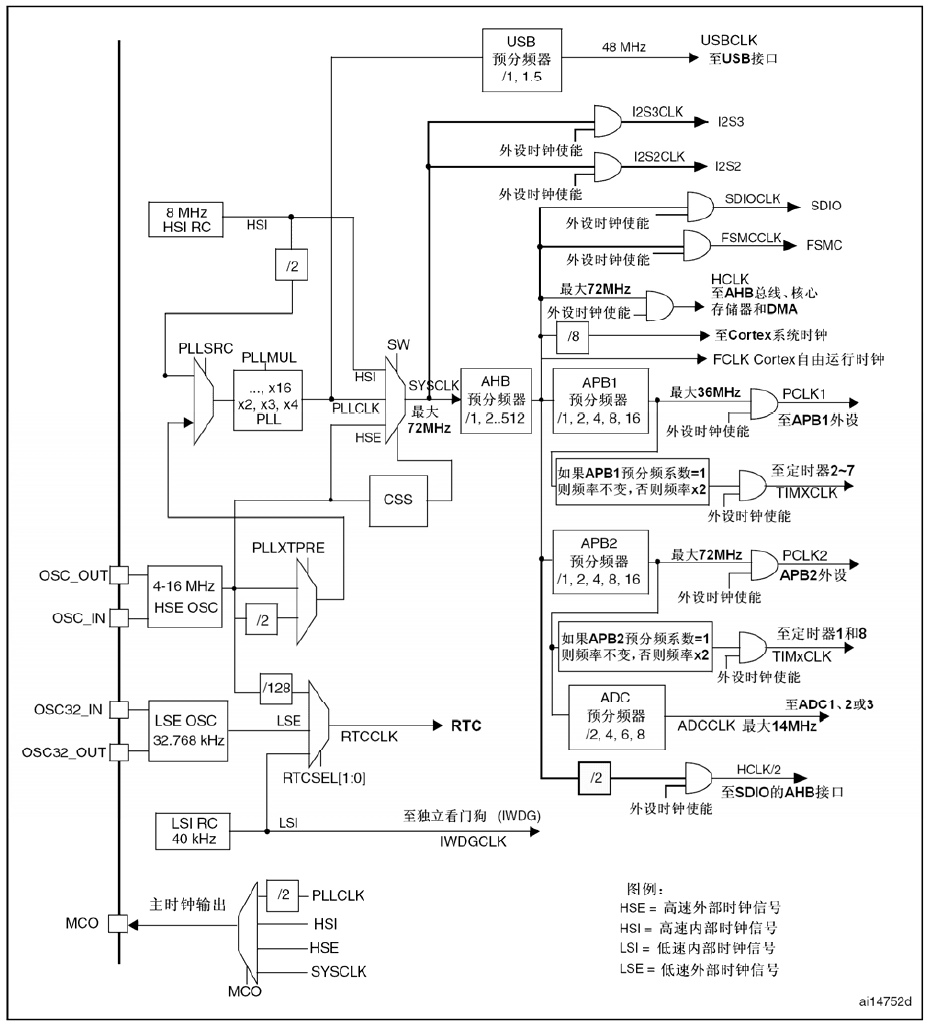

三種不同的時鐘源可用作系統(tǒng)時鐘(SYSCLOCK):

HIS振蕩器時鐘(由芯片內(nèi)部RC振蕩器提供)

HSE振蕩器時鐘(由芯片外部晶體振蕩器提供)

PLL時鐘(通過倍頻HIS或HSE振蕩器倍頻得到)

另外還有兩個時鐘源:

LSI內(nèi)部40kHz低速RC振蕩器時鐘,用于驅(qū)動獨(dú)立看門狗或選擇驅(qū)動RTC

LSE外部32.768kHz低速外部輸入時鐘,用于驅(qū)動RTC

時鐘模塊框圖如下:

|

圖1 時鐘樹框圖

|

1.當(dāng)HSI被用于作為PLL時鐘的輸入時,系統(tǒng)時鐘能得到的最大頻率是64MHz。

2.用戶可通過多個預(yù)分頻器配置AHB、高速APB(APB2)和低速APB(APB1)域的頻率。AHB和APB2域的最大頻率是72MHz。APB1域的最大允許頻率是36MHz。SDIO接口的時鐘頻率固定為HCLK/2。

3. RCC通過AHB時鐘(HCLK)8分頻后作為Cortex系統(tǒng)定時器(SysTick)的外部時鐘。通過對SysTick控制與狀態(tài)寄存器的設(shè)置,可選擇上述時鐘或Cortex(HCLK)時鐘作為SysTick時鐘。ADC時鐘由高速APB2時鐘經(jīng)2、4、6或8分頻后獲得。 定時器時鐘頻率分配由硬件按以下2種情況自動設(shè)置:

a. 如果相應(yīng)的APB預(yù)分頻系數(shù)是1,定時器的時鐘頻率與所在APB總線頻率一致。

b. 否則,定時器的時鐘頻率被設(shè)為與其相連的APB總線頻率的2倍。

4. FCLK是Cortex??-M3的自由運(yùn)行時鐘。詳情見ARM的Cortex??-M3技術(shù)參考手冊。

關(guān)于HSE、HIS、PLL、LSE、LSI時鐘特性及校準(zhǔn)直接參考STM32相關(guān)Datasheet。

系統(tǒng)時鐘配置過程:

配置過程主要對RCC_CR、RCC_CFGR、RCC_CIR這三個寄存器,進(jìn)行讀寫訪問,配置系統(tǒng)時鐘完成后進(jìn)行對要使用的相應(yīng)外設(shè)時鐘進(jìn)行使能和配置,不用的外設(shè)建議關(guān)閉相應(yīng)的外設(shè)時鐘(降低功耗)。

比較經(jīng)典的系統(tǒng)時鐘選擇配置為:使用外部8MHz的HSE時鐘源作為PLL時鐘輸入,PLL再進(jìn)行9倍頻得到72MHZ的時鐘作為系統(tǒng)時鐘輸出,具體實(shí)現(xiàn)過程如下:

1、置RCC_CR的HSION[0]位,啟動HIS時鐘。

2、清RCC_CFGR的MCO[26:24],ADCPRE[15:14],PPRE2[13:11],PPRE1[10:8],HPRE[7:4],SWS[3:2],SW[1:0]位,選擇默認(rèn)的HIS時鐘且設(shè)置相應(yīng)的時鐘不分頻。

3、清RCC_CR的PLLON[24],CSSON[19],HSEON[16]位,關(guān)閉PLL和HSE時鐘,且關(guān)閉時鐘檢測。

4、清RCC_CR的HSEBYP[18]位,說明HSE時鐘為外部的陶瓷晶體振蕩器,并非旁路模式。

5、清RCC_CFGR的USBPRE[22],PLLMUL[21:18],PLLXTPRE[17],PLLSRC[16]位,使HSE不分頻作為PLL的時鐘輸入,PLL的1.5倍頻作為USB的時鐘。

6、清RCC_CIR所有位,關(guān)閉全部的時鐘中斷。

7、置RCC_CR的HSEON[16]位,開啟HSE振蕩器。

8、檢測RCC_CR的HSERDY[17]位來檢測HSE振蕩器是否準(zhǔn)備就緒,若該位為1則接著往下配置,否則一直等待檢測直到該位被硬件置1或等待檢測時間結(jié)束。

9、清RCC_CFGR的HPRE[7:4]位,設(shè)置AHB預(yù)分頻值使SYSCLCK不分頻。

10、清RCC_CFGR的HPRE2[13:11]位,設(shè)置APB2時鐘(PCLK2)不分頻。

11、置RCC_CFGR的HPRE1[10:8]位為110,設(shè)置APB1時鐘(PCLK1)二分頻。

12、置RCC_CFGR的PLLMUL[21:18]位為0111,設(shè)置PLL9倍頻輸出,得到SYSCLK為72MHz。

13、置RCC_CR的PLLON[24]位,使能PLL時鐘。

14、檢測RCC_CR的PLLRDY[25]位,若為1表示PLL時鐘鎖定成功,為0表示鎖定未完成,繼續(xù)檢測等待直到該位被硬件置1.

15、置RCC_CFGR的SW[]1:0]位為10,選擇PLL輸出作為系統(tǒng)時鐘。

16、檢測RCC_CFGR的SWS[3:2]位,若為10表示PLL作為系統(tǒng)時鐘使用成功,否則一直等待直到該位為10,。

17、至此系統(tǒng)時鐘配置全部完成。

總結(jié)系統(tǒng)時鐘配置大體過程:

1、上電初始,開啟HSI振蕩器,關(guān)閉PLL及HSE,清RCC_CR及RCC_CFGR形影位為缺省值

2、開啟HSE振蕩器,等待HSE振蕩器啟動并進(jìn)入穩(wěn)定。

3、選擇HSE作為PLL時鐘輸入,配置好各個預(yù)分頻器相應(yīng)的預(yù)分頻系數(shù)。

4、啟動PLL時鐘,等待PLL時鐘準(zhǔn)備就緒。5、選擇PLL時鐘輸出作為系統(tǒng)時鐘輸入。